強誘電体の分極反転を考慮した強誘電体薄膜トランジスタ計測オプション

Transistor Task option for TFFT (Thin-Ferroelectric-Film-Transistor)

ラジアント社は不揮発性材料である強誘電体を使用した強誘電体メモリの評価装置を開発してきました。また、4/20/80 PNZT強誘電体を使った強誘電体薄膜トランジスタ(TFFT:Thin-Ferroelectric-Film-Transistor)を1992年に最初に作製し、強誘電体テスターを使用した様々な計測手順を開発してまいりました。

従来の金属酸化膜半導体電界効果トランジスタ(MOSFET:Metal-oxide-semiconductor field-effect transistor)の常誘電体酸化物を、強誘電体に置き換えた金属強誘電体膜半導体電界効果トランジスタ(MFSFET:Metal-ferroelectrics-semiconductor field-effect transistor)にすることで、不揮発性メモリ密度の高密度化が期待されるため研究が再燃しています。

また、HfOx系のような極薄膜での強誘電性発現からも研究が盛んになっています。

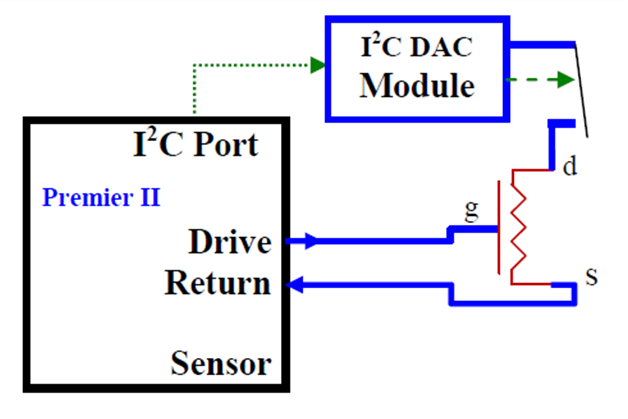

ラジアント社ではPrecision Premier II、Multiferroic II テスターシリーズに、I2C DACユニットを追加することで、強誘電体薄膜トランジスタに対する分極反転を考慮した様々な計測が可能になりました。

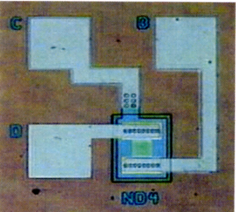

ここではラジアント社製のSFRAM (Static Ferroelectric RAM)を使用して実施した試験結果の一例を紹介します。下図はラジアント社製のSFRAM型トランジスタ素子の一例です。

ND4型トランジスタのデバイス・アーキテクチャー (40μ×40μ チャンネルサイズ)

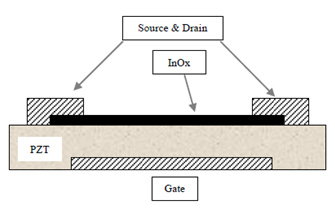

トランジスタ試験では、RETURN入力は常に電流入力として使用し、ソース(source)端子に接続され、DRIVE出力は常にゲート(gate)端子に接続されます。I2C DAC(D/A変換)で発生する電圧はトランジスタのドレイン(drain)端子にバイアス電圧として使われます。

下図の3端子の接続で不揮発性トランジスタ、TFFT、MFIS(Metal-FE-Insulator-Semiconductor)或いはEEPROMの何れに対しても、ベータ特性、ゲートヒステリシス、チャンネル電流ヒステリシス、保持力、疲労現象が評価できます。

強誘電体薄膜トランジスタと強誘電体テスターとの接続方式

従来のトランジスタ特性曲線描画装置は、Ids vs Vds 特性グラフを作成します。強誘電体ゲートトランジスタでは更なる特性評価が必要です。ゲート電圧の関数Ids vs Vgs自体が強誘電体由来のヒステリシス特性を示すためです。伝統的にはC vs Cox 試験で、CMOSトランジスタの特性を特徴付けします。各国の研究者は記憶特性の安定性を用いて、MFIS-FETの長期間にわたる保持力の予測を試みました。ラジアント社はメモリ電流特性の直接測定試験法を提供します。

同様に、強誘電体トランジスタの信頼性試験としてはFatigue (疲労特性)、Imprint(刷込み現象)に依る経時変化も追跡する必要があります。当然の事ですがRetention(保持力) も追跡対象です。これらの試験は全てVision LibraryにあるTransistor Current Taskを用いて実行が可能です。

1.強誘電体ゲートトランジスタの評価

1-1.Transistor Current Task(トランジスタ電流タスク)

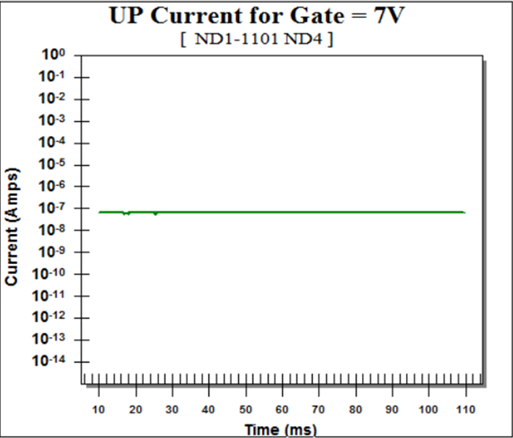

トランジスタのドレインとゲートに個別の一定電圧を指定時間入力し、チャンネルを通過する電流を計測し、計測時間vs電流を表示します。

代表的なトランジスタ電流タスクの計測結果

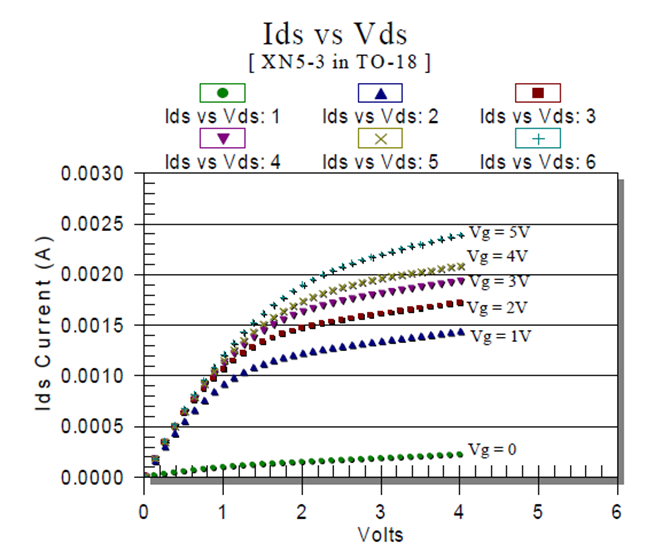

1-2.Transistor Curve Trace Task(トランジスタ特性曲線タスク)

一般的なIds vs Vds 特性曲線を書出すのが、この“Transistor Curve Trace Task”です。ゲート電圧を一定にしてドレイン電圧を変化させながら、チャンネルを通過する電流値を各ドレイン電圧点で計測します。

SRAM トランジスタのIds vs Vgs特性曲線

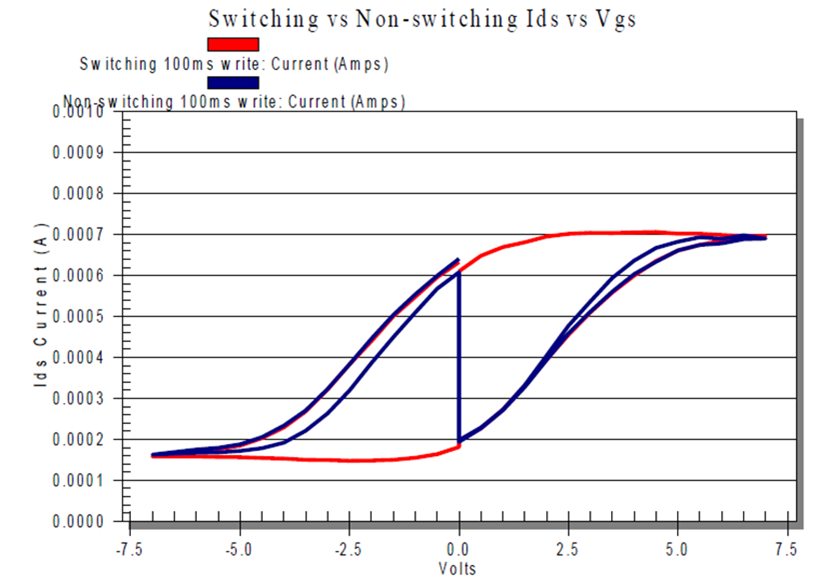

1-3.Transistor IV:(トランジスタIVタスク)

Ids vs Vgs測定用のタスク“Transistor IV Task”は強誘電体ドメインの影響でチャンネル導電率が変化する際の情報を提供します。ドレイン―ソース間電圧VdsをI2C DAC電圧で一定に保ち、ゲート電圧をDRIVE出力で変化させます。この計測はメモリトランジスタの強誘電体ゲートと半導体素子の品質に関する情報を提供します。メモリトランジスタではドレイン電圧Vdsはゲート強誘電体の分極状態に影響しない電圧に設定する必要があります。本SFRAMの場合は0.4Vを選択しています。

強誘電体メモリ評価に使用するHysteresis Taskは三角波を直接コンデンサに印加して、その結果発生する電荷を測定します。Transistor IV Taskはトランジスタのゲート電極に印加し、トランジスタの導通チャンネル部分の電流を測定します。

SFRAMによる分極反転の有と無のIV特性の一例

2.強誘電体ゲートコンデンサの評価

強誘電体ゲートトランジスタのゲートは強誘電体コンデンサとなります。このコンデンサ自身の電気特性については、下図の回路に切り替えて既存の計測が可能です(通常のDRIVE、RETURNとFE計測です)。

リレーを開いてゲートキャパシタンス測定をする際の試験設定

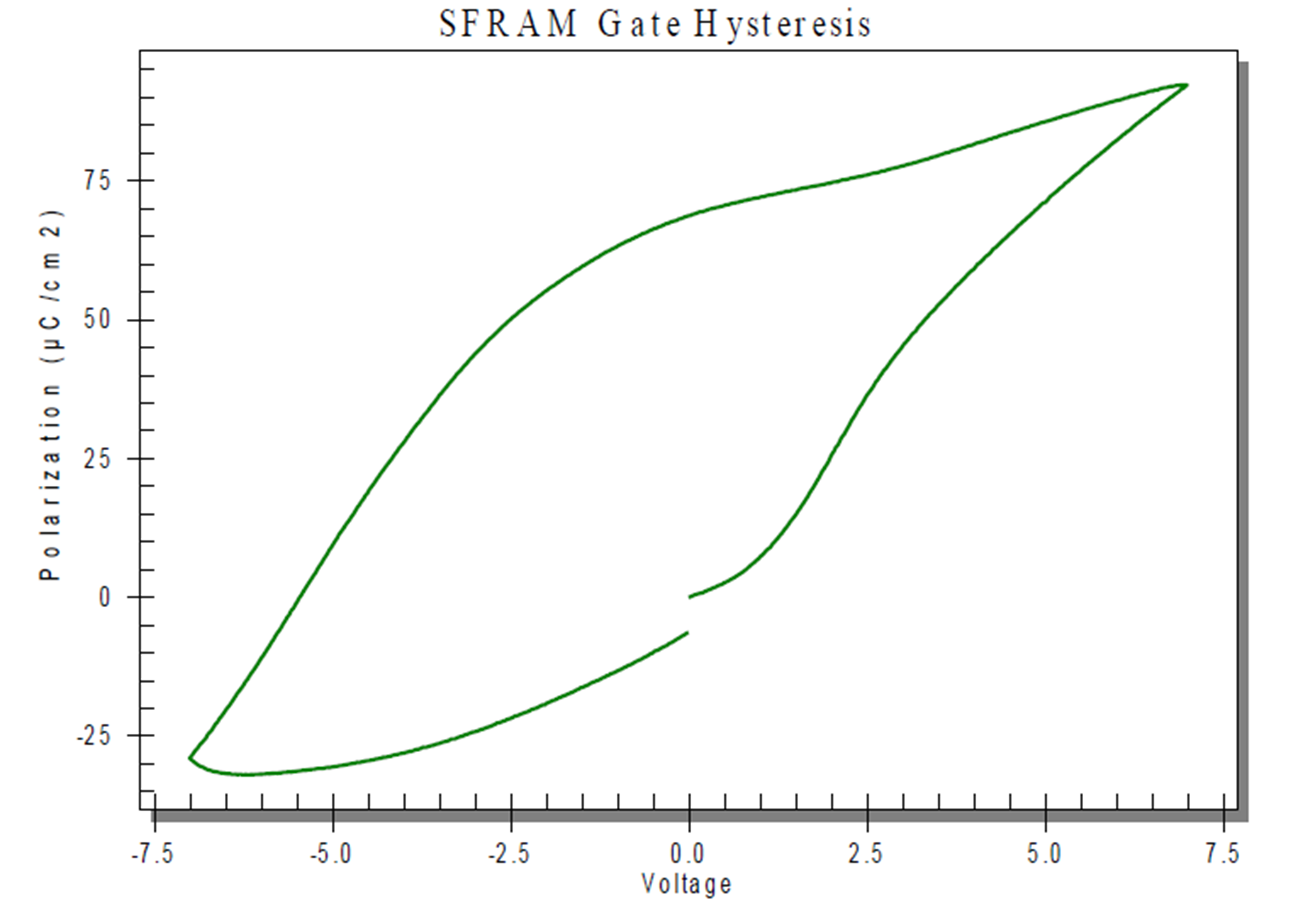

2-1.Gate Hysteresis:(ゲートヒステリシス)

強誘電体ゲートコンデンサ自身の分極反転スイッチングが計測可能です。

典型的なSFRAMのゲート分極ヒステリシス

2-2.Small Signal Capacitance(微小信号キャパシタンス)

Advanced CV Taskはゲートコンデンサにも実行できます。このタスクの結果はCMOSトランジスタの閾値電圧を決める目的で使用されるMOSCap CV測定と類似の結果を与えます。

2-3.Leakage(リーク電流)

ゲートコンデンサの漏れ電流を計測します。絶縁体部分の計測にのみ使用可能です。

2-4.Long Term Reliability(長期信頼性)

長期信頼性はメモリトランジスタ試験の中では最も重要な要素です。Fatigue (疲労)、Retention (保持力)、 Imprint (刷込み) はTransistor Current TaskとWaveform (波形発生)等を組み合わせ、研究者独自の実験手順、条件を作成し、評価ができます。

ご不明な点がございましたら、弊社までご連絡ください

トランジスタ計測オプションの詳しい資料が必要な方は、弊社ウェブサイトの「お問い合わせ」からご連絡ください。